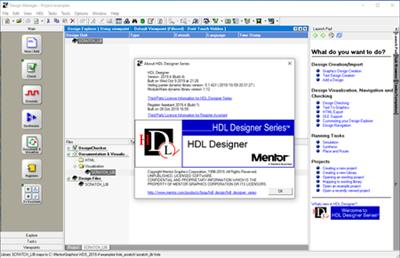

Mentor Graphics HDL Designer Series (HDS) 2019.4

"softddl.org"

7-12-2021, 15:27

-

Share on social networks:

-

Download for free: Mentor

-

Mentor Graphics HDL Designer Series (HDS) 2019.4 | 809.3 mb

Product:Mentor Graphics HDL Designer Series (HDS)

Version:2019.4 build 4

Supported Architectures:x64

Website Home Page :www.mentor.com

Languages Supported:english

System Requirements:PC *

Size:809.3 mb

The software developer Mentor Graphics, is pleased to announce the availability of HDL Designer Series (HDS) 2019.4 is a powerful HDL-based environment used by individual engineers and engineering teams worldwide to analyze, create and manage complex FPGA and ASIC designs.

Mentor Graphics HDL Designer Series (HDS) 2019.4 | 809.3 mb

Product:Mentor Graphics HDL Designer Series (HDS)

Version:2019.4 build 4

Supported Architectures:x64

Website Home Page :

www.mentor.comLanguages Supported:english

System Requirements:PC *

Size:809.3 mb

The software developer Mentor Graphics, is pleased to announce the availability of HDL Designer Series (HDS) 2019.4 is a powerful HDL-based environment used by individual engineers and engineering teams worldwide to analyze, create and manage complex FPGA and ASIC designs.

What's New in HDL Designer Series 2019.4

Summary

SVAssistant

- High Level Block Diagram Visualization

- Visualizer Integration

- Multiple Simulation Configuration

- SystemVerilog performance improvements

- Scalability Mode

- SystemVerilog Find References

HDL Designer

- Simplified Vivado Integration Flow

DesignChecker

- General bug fixing

Quality

- >50 Defects & Enhancements Resolved

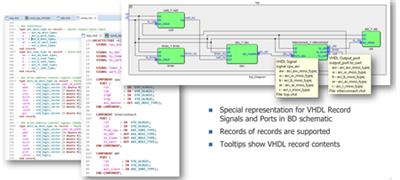

SVAssistant - High Level Block Diagram Visualization, VHDL Records

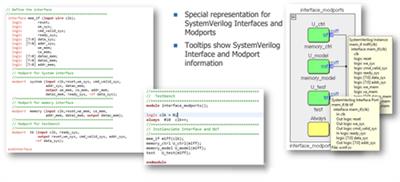

SVAssistant - High Level Block Diagram Visualization, SystemVerilog Interfaces

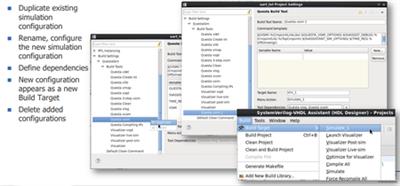

SVAssistant - Multiple Simulation Configurations

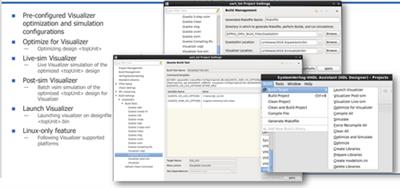

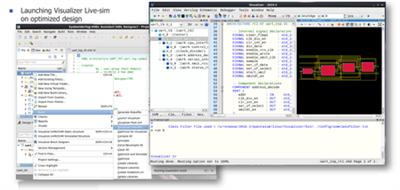

SVAssistant - Visualizer Integration

SVAssistant - Visualizer Integration

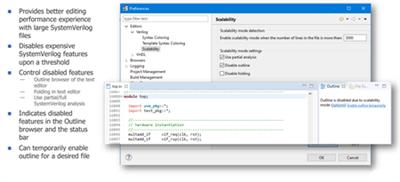

SVAssistant - SystemVerilog Scalability Mode

SVAssistant - SystemVerilog Find References

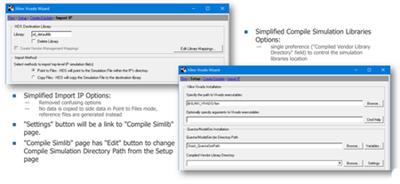

HDL Designer - Simplified Vivado Flow

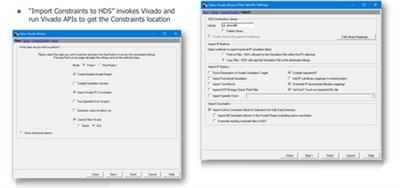

HDL Designer - Managing Vivado Flow Constraint Files

Vendor/Flow Supported Interfaces

- Microsemi Libero SoC 12.0, 12.1

- Microsemi Libero PolarFire 2.1 to 2.3

- Microsemi Libero IDE 9.1 to 9.2 SP3

- Intel Quartus Prime 17.x to 18.x 19.1 and 19.2 Pro Edition

- Altera MegaWizard Quartus II 13.0 to 14.0

- Altera Quartus SOPC Builder Quartus II 13.0 to 14.0

- Altera Quartus Synthesis Quartus II 14.1 to 15.0

- Cadence Incisive 10.2 to 11.10

- Lattice ISPLever 8.1 to 8.2

- Synopsys Synplify 2018_09 to 2019_09

- MGC Leonardo 2017a to 2018a

- MGC Precision 2018.1 to 2019.1.1

- MGC ModelSim/Questa 10.6x¹ to 2019.4

- Xilinx CORE Generator ISE 13.1 to 14.7

- Xilinx Platform Studio ISE 13.1 to 14.7

- Xilinx XST Synthesis ISE 13.1 to 14.7

- Xilinx Vivado 2018.2 to 2019.1

1. ModelSim/Questa 10.6 is not supported.

HDL Designeris a powerful HDL-based environment which delivers new approaches to design today's most complex FPGAs and ASICs. HDL Designer is used worldwide by individual engineers and engineering teams to create, analyze and manage the design of these amazing devices.

HDL Designer accelerates the productivity and predictability of the project by automating many flows and tasks. Automated rule checking, register generation and documentation and the powerful text, tabular and graphical creation editors save incredible amounts of engineering time and can minimize manually introduced errors. Tool integration and version management of the entire project help keep the team, tools and design process structured, but is still flexible enough through an API to augment existing design flows. Through this automation and project management, the overall quality of the project and resulting chip is improved and project risk greatly reduced.

By using HDL Designer, savings and cost avoidance can be recognized immediately through this automation and will continue with future projects through better design reuse, consistency of coding and improved documentation. For safety- and mission-critical projects, HDL Designer's design checking, version management, register generation and documentation support adherence to regulatory compliance mandates such as DO-254 and ISO 26262.

Mentor graphics : Block Diagram design in HDL Designer

Mentor Graphics Corporation, a Siemens business,is a world leader in electronic hardware and software design solutions, providing products, consulting services, and award-winning support for the world's most successful electronic, semiconductor, and systems companies. Corporate headquarters are located at 8005 S.W. Boeckman Road, Wilsonville, Oregon 97070-7777.

Product:Mentor Graphics HDL Designer Series (HDS)

Version:2019.4 build 4

Supported Architectures:x64

Website Home Page :

www.mentor.comLanguages Supported:english

System Requirements:PC *

Size:809.3 mb

Buy Premium From My Links To Get Resumable Support,Max Speed & Support Me

https://hot4share.com/fc77mmtqft4q/ay4p0.Mentor.Graphics.HDL.Designer.Series.HDS.2019.4.rar.html

https://rapidgator.net/file/946dc7720d083a0c1e1e433ab363c53c/ay4p0.Mentor.Graphics.HDL.Designer.Series.HDS.2019.4.rar.html

https://uploadgig.com/file/download/5c7c5d2Cb7037ed2/ay4p0.Mentor.Graphics.HDL.Designer.Series.HDS.2019.4.rar

https://nitro.download/view/064325C6273D69A/ay4p0.Mentor.Graphics.HDL.Designer.Series.HDS.2019.4.rar

The minimum comment length is 50 characters. comments are moderated