Digital System Design with High-Level Synthesis for FPGA

"softddl.org"

26-11-2020, 10:23

-

Share on social networks:

-

Download for free: Digital

-

MP4 | Video: h264, 1280x720 | Audio: AAC, 44.1 KHz, 2 Ch

Genre: eLearning | Language: English + .srt | Duration: 110 lectures (7h 47m) | Size: 8.72 GB

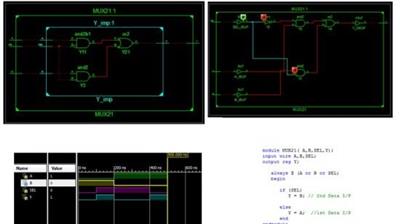

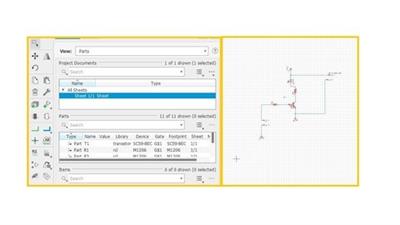

Combinational Circuits

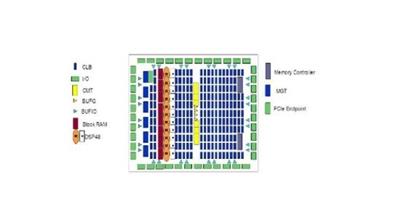

MP4 | Video: h264, 1280x720 | Audio: AAC, 44.1 KHz, 2 Ch Genre: eLearning | Language: English + .srt | Duration: 110 lectures (7h 47m) | Size: 8.72 GB Combinational Circuits What you'll learn: Designing combinational logic circuits with C/C++ language using the HLS approach Understanding the basic concepts of High-Level Synthesis (HLS) Using HLS concepts for designing combinational logic circuits HLS design flow for FPGAs Working with Xilinx Vivado-HLS and Vivado suite Toolsets How to generate RTL hardware IPs using Vivado-HLS Writing C-testbench in HLS Implementing two exciting projects with HLS Requirements Understanding the basic concepts of C/C++ coding Understanding the basic concepts of logic operators (e.g., AND, OR, XOR, SHIFT ) BASYS3 evaluation board Xilinx Vivado-HLS and Vivado (download Vivado HLx 2019.2: WebPACK and Editions for Windows or Linux) Description This course is an elementary introduction to high-level synthesis (HLS) design flow. The target of the course is describing, debugging and implementing combinational logic circuits on FPGAs using only C/C++ language without any help from HDLs (e.g., VHDL or Verilog). It uses the Xilinx HLS software and hardware platforms to demonstrate real examples and applications. This course is the first of its kind that builds the HLS design flow and skills along with the digital logic circuit concepts from scratch. Along the course, you will follow several examples describing the HLS concepts and techniques. The course contains numerous quizzes and exercises for you to practice and master the proposed methods and approaches. This course is the first of a series of courses on HLS in designing hardware modules and accelerating algorithms on a target FPGA. Whereas this course focuses on combinational circuits, the other courses in the series will explain how to use HLS in designing sequential logic circuits, algorithm acceleration, and hybrid CPU+ FPGA heterogeneous systems. Who this course is for Hardware engineers Software engineers who are interested in FPGAs Lecturers, researchers, professors who want to use FPGA-based HLS in lectures, courses or research Digital Logic enthusiasts Homepage https://www.udemy.com/course/hls-combinational-circuits/ Buy Premium From My Links To Get Resumable Support,Max Speed & Support Me

MP4 | Video: h264, 1280x720 | Audio: AAC, 44.1 KHz, 2 Ch Genre: eLearning | Language: English + .srt | Duration: 110 lectures (7h 47m) | Size: 8.72 GB Combinational Circuits What you'll learn: Designing combinational logic circuits with C/C++ language using the HLS approach Understanding the basic concepts of High-Level Synthesis (HLS) Using HLS concepts for designing combinational logic circuits HLS design flow for FPGAs Working with Xilinx Vivado-HLS and Vivado suite Toolsets How to generate RTL hardware IPs using Vivado-HLS Writing C-testbench in HLS Implementing two exciting projects with HLS Requirements Understanding the basic concepts of C/C++ coding Understanding the basic concepts of logic operators (e.g., AND, OR, XOR, SHIFT ) BASYS3 evaluation board Xilinx Vivado-HLS and Vivado (download Vivado HLx 2019.2: WebPACK and Editions for Windows or Linux) Description This course is an elementary introduction to high-level synthesis (HLS) design flow. The target of the course is describing, debugging and implementing combinational logic circuits on FPGAs using only C/C++ language without any help from HDLs (e.g., VHDL or Verilog). It uses the Xilinx HLS software and hardware platforms to demonstrate real examples and applications. This course is the first of its kind that builds the HLS design flow and skills along with the digital logic circuit concepts from scratch. Along the course, you will follow several examples describing the HLS concepts and techniques. The course contains numerous quizzes and exercises for you to practice and master the proposed methods and approaches. This course is the first of a series of courses on HLS in designing hardware modules and accelerating algorithms on a target FPGA. Whereas this course focuses on combinational circuits, the other courses in the series will explain how to use HLS in designing sequential logic circuits, algorithm acceleration, and hybrid CPU+ FPGA heterogeneous systems. Who this course is for Hardware engineers Software engineers who are interested in FPGAs Lecturers, researchers, professors who want to use FPGA-based HLS in lectures, courses or research Digital Logic enthusiasts Homepage https://www.udemy.com/course/hls-combinational-circuits/ Buy Premium From My Links To Get Resumable Support,Max Speed & Support Me  https://uploadgig.com/file/download/ff7daE9C0f630576/e4is2.Digital.System.Design.with.HighLevel.Synthesis.for.FPGA.part1.rar https://uploadgig.com/file/download/f4BbFac6e56b75fe/e4is2.Digital.System.Design.with.HighLevel.Synthesis.for.FPGA.part2.rar https://uploadgig.com/file/download/f29Fd2Ebb5836Cbd/e4is2.Digital.System.Design.with.HighLevel.Synthesis.for.FPGA.part3.rar https://uploadgig.com/file/download/87988ce12ef2c452/e4is2.Digital.System.Design.with.HighLevel.Synthesis.for.FPGA.part4.rar https://uploadgig.com/file/download/527d4Ce8dE2Ad901/e4is2.Digital.System.Design.with.HighLevel.Synthesis.for.FPGA.part5.rar https://uploadgig.com/file/download/ac550321616Ae14B/e4is2.Digital.System.Design.with.HighLevel.Synthesis.for.FPGA.part6.rar https://uploadgig.com/file/download/f884207301363350/e4is2.Digital.System.Design.with.HighLevel.Synthesis.for.FPGA.part7.rar

https://uploadgig.com/file/download/ff7daE9C0f630576/e4is2.Digital.System.Design.with.HighLevel.Synthesis.for.FPGA.part1.rar https://uploadgig.com/file/download/f4BbFac6e56b75fe/e4is2.Digital.System.Design.with.HighLevel.Synthesis.for.FPGA.part2.rar https://uploadgig.com/file/download/f29Fd2Ebb5836Cbd/e4is2.Digital.System.Design.with.HighLevel.Synthesis.for.FPGA.part3.rar https://uploadgig.com/file/download/87988ce12ef2c452/e4is2.Digital.System.Design.with.HighLevel.Synthesis.for.FPGA.part4.rar https://uploadgig.com/file/download/527d4Ce8dE2Ad901/e4is2.Digital.System.Design.with.HighLevel.Synthesis.for.FPGA.part5.rar https://uploadgig.com/file/download/ac550321616Ae14B/e4is2.Digital.System.Design.with.HighLevel.Synthesis.for.FPGA.part6.rar https://uploadgig.com/file/download/f884207301363350/e4is2.Digital.System.Design.with.HighLevel.Synthesis.for.FPGA.part7.rar  https://rapidgator.net/file/846ae9b26e1f0c696033f5a00ed95dc4/e4is2.Digital.System.Design.with.HighLevel.Synthesis.for.FPGA.part1.rar.html https://rapidgator.net/file/279f21b169a14e8b5e4bf8e76855a14b/e4is2.Digital.System.Design.with.HighLevel.Synthesis.for.FPGA.part2.rar.html https://rapidgator.net/file/835cd25b7fbd753a18cccafa35935c27/e4is2.Digital.System.Design.with.HighLevel.Synthesis.for.FPGA.part3.rar.html https://rapidgator.net/file/290483946716a28aef763147ef9a8265/e4is2.Digital.System.Design.with.HighLevel.Synthesis.for.FPGA.part4.rar.html https://rapidgator.net/file/c1ce77840401d62399ca6270b7d4494c/e4is2.Digital.System.Design.with.HighLevel.Synthesis.for.FPGA.part5.rar.html https://rapidgator.net/file/616ee6b66fb3317d4d320c70837e447d/e4is2.Digital.System.Design.with.HighLevel.Synthesis.for.FPGA.part6.rar.html https://rapidgator.net/file/c02efd7b0a0bb129618ee8039e4537fb/e4is2.Digital.System.Design.with.HighLevel.Synthesis.for.FPGA.part7.rar.html

https://rapidgator.net/file/846ae9b26e1f0c696033f5a00ed95dc4/e4is2.Digital.System.Design.with.HighLevel.Synthesis.for.FPGA.part1.rar.html https://rapidgator.net/file/279f21b169a14e8b5e4bf8e76855a14b/e4is2.Digital.System.Design.with.HighLevel.Synthesis.for.FPGA.part2.rar.html https://rapidgator.net/file/835cd25b7fbd753a18cccafa35935c27/e4is2.Digital.System.Design.with.HighLevel.Synthesis.for.FPGA.part3.rar.html https://rapidgator.net/file/290483946716a28aef763147ef9a8265/e4is2.Digital.System.Design.with.HighLevel.Synthesis.for.FPGA.part4.rar.html https://rapidgator.net/file/c1ce77840401d62399ca6270b7d4494c/e4is2.Digital.System.Design.with.HighLevel.Synthesis.for.FPGA.part5.rar.html https://rapidgator.net/file/616ee6b66fb3317d4d320c70837e447d/e4is2.Digital.System.Design.with.HighLevel.Synthesis.for.FPGA.part6.rar.html https://rapidgator.net/file/c02efd7b0a0bb129618ee8039e4537fb/e4is2.Digital.System.Design.with.HighLevel.Synthesis.for.FPGA.part7.rar.html  http://nitroflare.com/view/50E78A1F3C2C7FA/e4is2.Digital.System.Design.with.HighLevel.Synthesis.for.FPGA.part1.rar http://nitroflare.com/view/4B4036DF455B1FE/e4is2.Digital.System.Design.with.HighLevel.Synthesis.for.FPGA.part2.rar http://nitroflare.com/view/55CFB638FF62A5C/e4is2.Digital.System.Design.with.HighLevel.Synthesis.for.FPGA.part3.rar http://nitroflare.com/view/82D225277894B66/e4is2.Digital.System.Design.with.HighLevel.Synthesis.for.FPGA.part4.rar http://nitroflare.com/view/A7DD0D7D34A50B7/e4is2.Digital.System.Design.with.HighLevel.Synthesis.for.FPGA.part5.rar http://nitroflare.com/view/8F2051D0F4F2680/e4is2.Digital.System.Design.with.HighLevel.Synthesis.for.FPGA.part6.rar http://nitroflare.com/view/24789D9EF85B2EA/e4is2.Digital.System.Design.with.HighLevel.Synthesis.for.FPGA.part7.rar

http://nitroflare.com/view/50E78A1F3C2C7FA/e4is2.Digital.System.Design.with.HighLevel.Synthesis.for.FPGA.part1.rar http://nitroflare.com/view/4B4036DF455B1FE/e4is2.Digital.System.Design.with.HighLevel.Synthesis.for.FPGA.part2.rar http://nitroflare.com/view/55CFB638FF62A5C/e4is2.Digital.System.Design.with.HighLevel.Synthesis.for.FPGA.part3.rar http://nitroflare.com/view/82D225277894B66/e4is2.Digital.System.Design.with.HighLevel.Synthesis.for.FPGA.part4.rar http://nitroflare.com/view/A7DD0D7D34A50B7/e4is2.Digital.System.Design.with.HighLevel.Synthesis.for.FPGA.part5.rar http://nitroflare.com/view/8F2051D0F4F2680/e4is2.Digital.System.Design.with.HighLevel.Synthesis.for.FPGA.part6.rar http://nitroflare.com/view/24789D9EF85B2EA/e4is2.Digital.System.Design.with.HighLevel.Synthesis.for.FPGA.part7.rar

The minimum comment length is 50 characters. comments are moderated