Udemy - FPGA Design Glitch in Counters - Analysis using Simulator (updated)

"softddl.org"

13-01-2021, 12:48

-

Share on social networks:

-

Download for free: Udemy - FPGA

-

Genre: eLearning | MP4 | Video: h264, 1280x720 | Audio: aac, 48000 Hz

Language: English | SRT | Size: 2.57 GB | Duration: 3h 50m

Genre: eLearning | MP4 | Video: h264, 1280x720 | Audio: aac, 48000 Hz

Language: English | SRT | Size: 2.57 GB | Duration: 3h 50m

What you'll learn

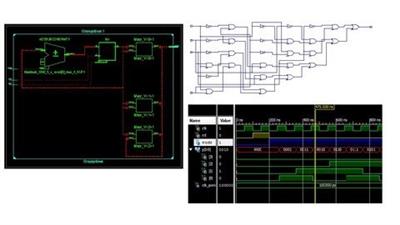

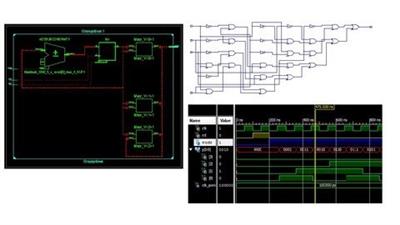

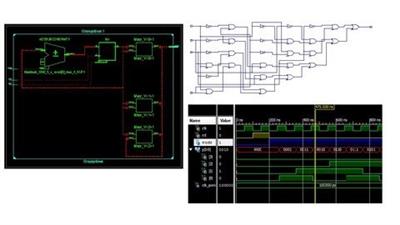

VHDL Programming for Various types of Synchronous Counters for Xilinx FPGA , it's Synthesis & Comparative Glitch Analysis using Timing Simulation of Xilinx ISE Tool

Requirements

Basic knowledge of Digital - Sequential Logic Design Basic knowledge of any Programming Language ( Ex. C Programming ) Basic knowledge of VHDL Programming is advantageous

Description

Hello Dear Student ,

I welcome you , for Enrolling this Course .

In this Course , You will Learn to write Programs in VHDL for various types of Synchronous Counters & Synthesize it , and read the RTL Schematic as well as Technology Schematic .

You will Learn , to Write a VHDL Test Bench for Counters and run the Behavioral Simulation .

You will Learn , analyzing the Glitch Behavior & Pattern for Various Counter Designs using Timing Simulator using Xilinx ISE Tool .

You will understand , to compare the Performances of Glitch for various Counter Designs .

Who this course is for:

Beginners , Hobbyists , Students of Engineering / Technology from Electronics / Computer Engineering / Electrical Engineering Branch

Homepage

https://www.udemy.com/course/fpga-design-glitch-in-counters-analysis-using-simulator/Buy Premium From My Links To Get Resumable Support,Max Speed & Support Me

https://uploadgig.com/file/download/85B2c6e84a767178/t3m93.FPGA.Design..Glitch.in.Counters..Analysis.using.Simulator.updated.part1.rar

https://uploadgig.com/file/download/dFfe7c698F1daDd7/t3m93.FPGA.Design..Glitch.in.Counters..Analysis.using.Simulator.updated.part2.rar

https://uploadgig.com/file/download/ad6E6b6fa1C56ffE/t3m93.FPGA.Design..Glitch.in.Counters..Analysis.using.Simulator.updated.part3.rar

https://rapidgator.net/file/674058e161bd34064c4ceb1e3084c9db/t3m93.FPGA.Design..Glitch.in.Counters..Analysis.using.Simulator.updated.part1.rar.html

https://rapidgator.net/file/77898344961f9420b8b50bf34aa2415d/t3m93.FPGA.Design..Glitch.in.Counters..Analysis.using.Simulator.updated.part2.rar.html

https://rapidgator.net/file/0a630d4a2e00260b1813abc8570466ac/t3m93.FPGA.Design..Glitch.in.Counters..Analysis.using.Simulator.updated.part3.rar.html

http://nitroflare.com/view/7B5B921E9F33FFA/t3m93.FPGA.Design..Glitch.in.Counters..Analysis.using.Simulator.updated.part1.rar

http://nitroflare.com/view/ADFFAF65E167F97/t3m93.FPGA.Design..Glitch.in.Counters..Analysis.using.Simulator.updated.part2.rar

http://nitroflare.com/view/EAEC78EE240AEF7/t3m93.FPGA.Design..Glitch.in.Counters..Analysis.using.Simulator.updated.part3.rar

Links are Interchangeable - No Password - Single Extraction

The minimum comment length is 50 characters. comments are moderated